# 日本国特許庁 JAPAN PATENT OFFICE

別紙添付の書類に記載されている事項は下記の出願書類に記載されている事項と同一であることを証明する。

This is to certify that the annexed is a true copy of the following application as filed with this Office

出願年月日

Date of Application:

2000年 9月 4日

出 願 番 号

Application Number:

特願2000-267851

出 願 人

Applicant(s):

株式会社半導体エネルギー研究所

2001年 6月12日

特許庁長官 Commissioner, Japan Patent Office

# 特2000-267851

【書類名】

特許願

【整理番号】

P005193

【提出日】

平成12年 9月 4日

【あて先】

特許庁長官 及川 耕造 殿

【発明者】

【住所又は居所】 神奈川県厚木市長谷398番地 株式会社半導体エネル

ギー研究所内

【氏名】

大沼 英人

【発明者】

【住所又は居所】 神奈川県厚木市長谷398番地 株式会社半導体エネル

ギー研究所内

【氏名】

上原 一郎

【特許出願人】

【識別番号】

000153878

【氏名又は名称】 株式会社半導体エネルギー研究所

【代表者】

山崎 舜平

【手数料の表示】

【予納台帳番号】 002543

【納付金額】

21,000円

【提出物件の目録】

【物件名】

明細書 1

【物件名】

図面 1

【物件名】

要約書 1

【プルーフの要否】 要

# 【書類名】明細書

【発明の名称】半導体装置の製造方法

# 【特許請求の範囲】

#### 【請求項1】

光強度低減手段を有するフォトマスクまたはレチクルを使用してゲート電極形成用のレジストパターンを形成する第1の工程と、前記レジストパターンをマスクとしてドライエッチング処理し、膜厚の厚い領域と端部の膜厚の薄い領域を有するゲート電極を形成する第2の工程と、一導電型の不純物をイオン注入して、前記ゲート電極の外側領域に対応する半導体層または半導体基板に第1の不純物領域を形成し、同時に前記ゲート電極の端部に存在する膜厚の薄い領域に対応する半導体層または半導体基板に第2の不純物領域を形成する第3の工程と、前記ゲート電極の端部の膜厚の薄い領域をドライエッチング処理し、前記ゲート電極の端部を後退させる第4の工程と、前記レジストパターンを除去する第5の工程とを有することを特徴とする半導体装置の製造方法。

# 【請求項2】

請求項1に於いて、前記光強度低減手段は複数のスリット部を有する回折格子 パターンで構成されていることを特徴とする半導体装置の製造方法。

#### 【請求項3】

請求項1に於いて、前記光強度低減手段は半透膜で構成されていることを特徴とする半導体装置の製造方法。

#### 【請求項4】

請求項1に於いて、前記光強度低減手段に於ける露光光の透過率は、当該マスクパターン端部からの距離に比例して増加する様に構成されていることを特徴とする半導体装置の製造方法。

# 【請求項5】

請求項1に於いて、前記第1の不純物領域はソース及びドレイン領域となる高 濃度不純物領域であり、前記第2の不純物領域は低濃度不純物領域であることを 特徴とする半導体装置の製造方法。

### 【請求項6】

請求項1に於いて、前記半導体装置は多結晶薄膜トランジスタで構成されていることを特徴とする半導体装置の製造方法。

# 【請求項7】

請求項1に於いて、前記半導体装置はMOS型トランジスタで構成されていることを特徴とする半導体装置の製造方法。

# 【発明の詳細な説明】

[0001]

# 【発明の属する技術分野】

本発明は薄膜トランジスタ(以下、TFTと略記)及びMOSトランジスタで構成された回路を有する半導体装置の製造法に関するものである。半導体装置としては、例えばTFTで構成された液晶ディスプレイ及びEL(エレクトロルミネッセンス)ディスプレイ等の電気光学装置があり、MOSトランジスタで構成されたLSIがある。

[0002]

# 【従来の技術】

近年、TFTを利用したアクティブマトリクス型の液晶ディスプレイ技術が注目されている。アクティブマトリクス表示はパッシブマトリクス表示に比べ、応答速度、視野角、コントラストの点で有利な為、現在のノートパソコン、液晶テレビ等の主流になっている。

[0003]

TFTは非晶質シリコンまたは多結晶シリコンをチャネル層とするものが一般 的である。特に低温プロセス(一般に600℃以下)のみで製造される多結晶シ リコンTFTは、低価格化、大面積化と同時に、電子または正孔が大きな電界移 動度を有する為、液晶ディスプレイに用いた場合、画素用トランジスタだけでな く周辺回路であるドライバーの一体化が達成できる特徴があり、各液晶ディスプ レイメーカーで開発が進められてきた。

[0004]

しかし、多結晶シリコンTFTの場合、連続駆動させると移動度やオン電流(TFTがオン状態の場合に流れる電流)の低下及びオフ電流(TFTがオフ状態

2

の場合に流れる電流)の増加等の劣化現象が観測されることがあり、信頼性上大きな問題である。この現象はホットキャリア現象と呼ばれており、ドレイン近傍の高電界により発生したホットキャリアの仕業であることが知られている。

# [0005]

ところで、このホットキャリア現象は、最初にMOSトランジスタに於いて発見された現象である。この為、ホットキャリア対策として、これまで様々な基礎検討が行われてきており、設計ルール1.5μm以下のMOSトランジスタでは、ドレイン近傍の高電界によるホットキャリア現象の対策として、LDD (Lightly Doped Drain) 構造が採用されている。LDD構造では、ゲート側壁のサイドウォールを利用してドレイン端部に低濃度不純物領域(nー領域)を設け、ドレイン接合の不純物濃度に傾斜を持たせることによりドレイン近傍の電界集中を緩和している。

# [0006]

しかし、LDD構造の場合、シングルドレイン構造に比べ、ドレイン耐圧はかなり向上するが、低濃度不純物領域(n-領域)の抵抗が大きい為、ドレイン電流が減少するという難点が有る。また、サイドウォールの真下に高電界領域が存在し、そこで衝突電離が最大になり、ホットエレクトロンがサイドウォールに注入される為、低濃度不純物領域(n-領域)が空乏化し、更に抵抗が増加するLDD特有の劣化モードが問題になっている。チャネル長の縮小に伴い、以上の問題が顕在化してきた為、0.5μm以下のMOSトランジスタでは、この問題を克服する構造として、ゲート電極の端部にオーバーラップして低濃度不純物領域(n-領域)を形成するGOLD(Gate-drain Overlapped LDD)構造が考案され採用されている。

### [0007]

多結晶シリコンTFTに於いても、MOSトランジスタと同様にドレイン近傍 の高電界を緩和する目的で、LDD構造及びGOLD構造の採用が検討されてい る。LDD構造の場合は、ゲート電極の外側領域に対応する多結晶シリコン層に 低濃度不純物領域(n-領域)とその更に外側にソース及びドレイン領域となる 高濃度不純物領域(n+領域)を形成しており、オフ電流値を抑える効果は高い が、ドレイン近傍の電界緩和によるホットキャリア対策効果は小さいという特徴がある。一方、GOLD構造の場合は、LDD構造の低濃度不純物領域(n-領域)がゲート電極端部とオーバーラップする様に形成されており、LDD構造に比べホットキャリア対策効果は大きいが、オフ電流値が大きくなるという点が難点である。

[0008]

# 【発明が解決しようとする課題】

多結晶シリコンTFT及びMOSトランジスタに於けるLDD構造とGOLD構造のソースドレイン領域となる高濃度不純物領域(n+領域)及びその内側の低濃度不純物領域(n-領域)の形成は、従来、ゲート電極をマスクにセルフアラインで形成しており、フォトリソグラフィ工程の増加を抑制できる利点があるが、ゲート電極が2層構造となる為、成膜工程とエッチング工程が複雑になるという課題がある。

# [0009]

また、半導体装置には様々な回路が内包されており、回路によってはホットキャリア対策効果に優れたGOLD構造が適している場合もあれば、オフ電流値の小さいLDD構造が適している場合もあり、場合によっては、シングルドレイン構造が適している場合もある。LDD構造及びGOLD構造の形成は、ドライエッチング等のプロセスのみで形成する為、半導体装置内のトランジスタ構造が全て同一構造となり、回路毎にシングルドレイン構造とLDD構造及びGOLD構造を別々に形成することが困難な点が課題である。

# [0010]

また、GOLD構造に於いては、低濃度不純物領域(n-領域)の長さが、基本的にサイドエッチング等のエッチングにより形成される第1層ゲート電極膜のみが存在する領域で決まる為、低濃度不純物領域(n-領域)の長さに制約が生じ、またはその長さを十分に確保できない等の課題が有る。

本発明は、上記課題を解決することのできる半導体装置の製造法を提供することを目的とする。

[0011]

# 【課題を解決する為の手段】

フォトリソグラフィ工程で使用されるゲート電極形成用フォトマスクまたはレチクルに於いて、ゲート電極形成用マスクパターンの片側または両側の端部に露光光の光強度を低減する機能を有する光強度低減手段である補助パターンを設置する。前記補助パターンでの露光光の光強度の低減機能を有する具体的パターンとしては、解像限界以下のライン/スペースから成る複数のスリット部を有する回折格子パターンと露光光の透過率を低減する半透膜が有る。そして、前記補助パターンでの透過率は一様でなく傾斜しており、ゲート電極形成用マスクパターンからの距離に比例して、透過率が徐々に増加する様に構成されている。

# [0012]

尚、回折格子パターンに於いては、スリット部のピッチとスリット幅の調整により透過光の光強度の調整が可能であり、ゲート電極形成用マスクパターン端部からの距離に比例して、透過率を増加させる為、スリット幅が徐々に大きくなる構造となっている。また、半透膜に於いては、半透膜の膜厚または透過率自体の調整により透過光の光強度の調整が可能であり、ゲート電極形成用マスクパターン端部からの距離に比例して、半透膜の膜厚が徐々に薄くなるか、または半透膜の透過率自体が徐々に増加する構造となっている。

### [0013]

ところで、本フォトリソグラフィ工程で使用されるレジストはネガ型レジスト が適用困難である為、当該ゲート電極形成用フォトマスクまたはレチクルのパタ ーン構成は、ポジ型レジストを前提にしている。

# [0014]

この様な構成の前記ゲート電極形成用フォトマスクまたはレチクルを用いて露 光した場合、ゲート電極形成用マスクパターンの主パターンの領域は、遮光部で ある為に光強度はゼロであり、前記補助パターンの更に外側の領域は透光部であ る為、光強度は100%である。一方、遮光部と透光部の境界領域である前記補 助パターンの領域では、光強度が10~70%の範囲で、ゲート電極形成用マス クパターンからの距離に比例して、透過率が徐々に増大する様に構成されている 。そして、ゲート電極形成用フォトマスクまたはレチクルをフォトリソグラフィ 工程に適用することにより、現像後レジストパターンの片側または両側の端部に 於ける膜厚が、通常に比べ10~60%の範囲内で薄く形成され、且つ端部に近 づく程、レジスト膜厚が徐々に薄くなるテーパー形状領域を有したレジストパタ ーン形状が形成されている。

# [0015]

ところで、ステッパ等の縮小投影露光装置を使用する単波長露光の場合、露光 光の位相が或る程度揃っているパーシャルコヒーレント光である為、補助パター ンとして半透膜を適用すると、半透膜がハーフトーン型位相シフタとして作用す ることが考えられる。この場合は、隣接する露光光との間の位相が180°程度 に反転しない様に半透膜の膜厚の調整には注意が必要である。従って、縮小投影 露光装置に適用されるレチクルの場合には、補助パターンとして、半透膜を適用 する上に於いて、位相シフト量と透過率の両方を考慮して、半透膜の膜厚を調整 する。

# [0016]

また、本発明のフォトリソグラフィ工程に於いては、ポジ型レジストのみを前提にしていることは既に述べたが、ここではその理由について説明する。ネガ型レジストの場合はポジ型レジストと逆に、ゲート電極形成用フォトマスクまたはレチクルの主パターン領域が透光部で、補助パターンの外側の領域が遮光部であり、透光部と遮光部との境界領域である補助パターン領域が光強度低減機能を有する領域(光強度を10~70%程度の範囲で低減)のパターン構成となっている。前記パターン構成を有するフォトマスクまたはレチクルを用いて、ネガ型レジストを露光した場合、補助パターン領域にはレジストパターン形成に必要十分な露光エネルギーが照射されない為、レジスト膜の上層部のみ露光された状態となり、下層部は未露光または露光不足の状態となっている。この状態のネガ型レジストを現像した場合、当該領域のレジスト膜の上層部は現像液に不溶であるが、下層部が現像液に可溶である為、レジスト膜の下層部のみをレジスト残膜とする良好なパターン形成ができない。

### [0017]

上記理由の為、本発明のフォトリソグラフィ工程に於いては、ネガ型レジスト

は適用困難であり、ポジ型レジストのみの適用となっている。

[0018]

上記フォトリソグラフィ工程により、レジストパターンの片側または両側のパターン端部に近づく程、レジスト膜厚の薄くなったテーパー形状領域を有したゲート電極形成用レジストパターンを形成した後、第1のドライエッチング処理を行う。この所定時間のドライエッチング処理により、ゲート電極膜とレジスト膜との選択比の問題で、徐々にレジスト膜がエッチングされる為、ドライエッチングの途中で、前記テーパー形状領域でのレジストパターン端部のレジスト膜厚の薄い領域から下地のゲート電極膜が徐々に露出し、当該領域の端部からゲート電極膜のエッチングが進行することになる。当該領域のゲート電極膜の残膜厚が初期膜厚の5~30%程度の所定膜厚になる様にドライエッチングした後、片側または両側のゲート電極端部に近づく程、ゲート電極膜厚の薄くなるテーパー形状領域を有したゲート電極構造が形成される。尚、ゲート電極から露出している下地のゲート絶縁膜は、ドライエッチングされ、ある程度薄くなっている。

# [0019]

次に前記ゲート電極をマスクに n 型不純物の高濃度イオン注入することにより、ゲート電極の外側に対応する多結晶シリコン膜または半導体基板にソース及びドレイン領域となる高濃度不純物領域(n + 領域)が形成され、当該ゲート電極の片側または両側のゲート電極膜の薄くなったテーパー形状領域に対応する多結晶シリコン膜または半導体基板に低濃度不純物領域(n - 領域)が形成される。この際、ゲート電極の膜厚の違いを考慮し、イオン注入時の加速電圧とイオン注入量を適宜選択することにより、ゲート電極の外側領域に対応する多結晶シリコン膜または半導体基板に高濃度不純物領域(n + 領域)を形成し、またゲート電極の端部に於けるゲート電極膜厚の薄いテーパー形状領域に対応する多結晶シリコン膜または半導体基板に低濃度不純物領域(n - 領域)を同時に形成することができる。尚、ゲート電極端部の前記テーパー形状領域では、ゲート電極の端部に近づく程、ゲート電極膜厚が徐々に薄くなっている為、スルードープでイオン注入される低濃度不純物領域(n - 領域)の不純物濃度には濃度勾配が存在し、ゲート電極の端部即ちソース及びドレイン領域の端部に近づく程、徐々に不純物

濃度が高くなる傾向を有している。

[0020]

ここで、イオン注入という用語の定義について、明確にする。世間一般では、 質量分離した不純物イオンの場合にイオン注入、質量分離しない不純物イオンの 場合にはイオンドープの用語が適用されている。本明細書に於いては、イオン注 入とイオンドープの用語の使い分けは特に行わず、不純物イオンの質量分離に関 係なく、イオン注入で代表している。

[0021]

次に第2のドライエッチング処理を行う。この所定時間のドライエッチング処理により、ゲート電極端部の前記テーパー形状領域はドライエッチングされる。その結果、テーパー形状領域のゲート電極膜厚は更に薄くなり、テーパー形状領域の端部であるゲート電極端部は後退する。よって、濃度勾配を有した前記低濃度不純物領域(n-領域)は、ゲート電極とオーバーラップしている領域(Lov領域と定義)とオーバーラップしてない領域(Loff領域と定義)に区分される。この際、ドライエッチング処理条件を適宜変更することにより、ゲート電極の寸法を前記テーパー形状領域の範囲内で自由に調整することができる。即ち、前記テーパー形状領域の範囲内で、Lov領域の寸法とLoff領域の寸法を自由に調整することができる。また、ゲート電極から露出した下地のゲート絶縁膜は、ドライエッチングにより更に薄くなっている。この後、ゲート電極のドライエッチングマスクである不要なレジストパターンは、除去される。

[0022]

尚、Lov領域は、ホットキャリア対策に効果があり、Loff領域はオフ電流の抑制に効果があることが知られている。ここで形成されたトランジスタはホットキャリア対策に有効なGOLD構造トランジスタであり、オフ電流の抑制に効果の有るLoff領域を有している為、ある程度のオフ電流の抑制効果は期待されるが、オフ電流の抑制効果に限って言うと、後述のLDD構造トランジスタの方が有利である。

[0023]

以上はGOLD構造トランジスタの形成法について記載したものであるが、半

導体装置には様々な回路が内包されており、回路によってはホットキャリア対策に有効なGOLD構造トランジスタが適している場合もあれば、オフ電流の抑制に有効なLDD構造トランジスタが適している場合もある。また場合によっては、シングルドレイン構造トランジスタが適している場合もある。よって、回路毎にGOLD構造とLDD構造とシングルドレイン構造トランジスタを別々に形成する方法について、以下に記載する。

# [0024]

最初に、ゲート電極形成用レジストパターンを形成する。この際、適用するフォトマスクまたはレチクルに於いて、GOLD構造形成領域とLDD構造形成領域に対応するゲート電極形成用マスクパターンには光強度低減機能を有する補助パターンを設置し、シングルドレイン構造形成領域に対応するゲート電極形成用マスクパターンには前記補助パターンを設置しないパターン構成とする。この結果、GOLD構造形成領域とLDD構造形成領域のレジストパターンには、端部に近づく程、レジスト膜厚の徐々に薄くなるテーパー形状領域が形成され、シングルドレイン構造形成領域のレジストパターンには前記テーパー形状領域が存在せず、矩形形状のレジストパターンが形成される。

#### [0025]

尚、GOLD構造形成領域とLDD構造形成領域のレジストパターンに於ける前記テーパー形状領域の寸法は、最終的に形成されるGOLD構造及びLDD構造トランジスタに於ける低濃度不純物領域(n-領域)の寸法を考慮し、当該マスクパターンの前記補助パターン領域の寸法を調整することにより、適切な長さに形成される。この際、GOLD構造とLDD構造トランジスタの低濃度不純物領域(n-領域)の寸法は、各々対応するマスクパターンに設置された前記補助パターン領域の寸法を調整することにより、自由に設定可能である。またGOLD構造形成領域とLDD構造形成領域のレジストパターンに於ける前記テーパー形状領域の膜厚は、各々対応するマスクパターンに設置された補助パターン領域の透過率を10~70%の範囲で調整することにより、適切なレジスト膜厚(初期膜厚に対し10~60%の範囲)に形成される。

[0026]

次に第1のドライエッチング処理を行う。この所定時間のドライエッチング処理により、GOLD構造形成領域とLDD構造形成領域に於いては、片側または両側のゲート電極端部に近づく程、ゲート電極膜厚の薄くなるテーパー形状領域を有したゲート電極が形成される。一方、シングルドレイン構造形成領域に於いては、矩形形状のゲート電極が形成される。

# [0027]

次に、前記ゲート電極をマスクに n 型不純物の高濃度イオン注入を行う。 G O L D 構造形成領域と L D D 構造形成領域に於いては、ゲート電極の外側に対応する多結晶シリコン膜または半導体基板にソース及びドレイン領域となる高濃度不純物領域(n+領域)が形成され、ゲート電極膜厚の薄い前記テーパー形状領域に対応する多結晶シリコン膜または半導体基板に低濃度不純物領域(nー領域)が形成される。一方、シングルドレイン構造形成領域に於いては、ソース及びドレイン領域となる高濃度不純物領域(n+領域)のみが形成される。

# [0028]

次に、第2のドライエッチング処理を行う。この所定時間のドライエッチング処理により、GOLD構造形成領域に於いては、ゲート電極端部の前記テーパー形状領域がドライエッチングされ、テーパー形状領域のゲート電極膜厚は更に薄くなり、テーパー形状領域の端部であるゲート電極端部は後退する。ゲート電極端部がある程度後退するまでドライエッチング処理を行った後、前記低濃度不純物領域(nー領域)は、ゲート電極とオーバーラップしているLov領域とオーバーラップしていないLoff領域に区分される。LDD構造形成領域に於けるゲート電極の前記テーパー形状領域も、GOLD構造形成領域の場合と同様にドライエッチングされる。一方、シングルドレイン構造形成領域のゲート電極も同様にドライエッチングされるが、当該ゲート電極が矩形形状である為、下地のゲート絶縁膜が更にエッチングされるだけである。この後、ゲート電極のドライエッチングマスクである不要なレジストパターンは、除去される。

#### [0029]

尚、前記第2のドライエッチング処理及びドライエッチングのマスクであるレジストパターンの除去が終了した段階で、LDD構造形成領域に於けるゲート電

極の前記テーパー形状領域が残存している場合と消失している場合で、これからの処理プロセスが変化する為、以下に別々に記載する。

[0030]

前記第2のドライエッチング処理による所定時間のドライエッチング後に、LDD構造形成領域に於けるゲート電極の前記テーパー形状領域が残存している場合は、前記テーパー形状領域を選択的にドライエッチングし、前記テーパー形状領域を除去する必要がある。この為、LDD構造形成領域のみを開口する様に新規にレジストパターンを形成し、第3のドライエッチング処理を行う。この所定時間のドライエッチング処理により、前記テーパー形状領域は選択的に除去され、矩形形状のゲート電極が形成される。この結果、ゲート電極の外側に対応する多結晶シリコン膜または半導体基板に、低濃度不純物領域(nー領域)と高濃度不純物領域(n+領域)を有するLDD構造トランジスタが形成される。この後、ドライエッチングマスクである前記レジストパターンは、除去される。

[0031]

一方、前記第2のドライエッチング処理による所定時間のドライエッチング後に、LDD構造形成領域に於けるゲート電極の前記テーパー形状領域が消失している場合は、LDD構造形成領域のみを開口するレジストパターンの形成と第3のドライエッチング処理は不要である。この場合は、前記第2のドライエッチング処理及びドライエッチングのマスクであるレジストパターンの除去が終了した段階で、既にLDD構造トランジスタの形成は完了していることになる。

[0032]

以上の製造工程により、半導体装置の回路毎にGOLD構造とLDD構造とシングルドレイン構造トランジスタを別々に形成することができる。

[0033]

本発明は、マスクパターンに光強度低減手段である補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルを適用するフォトリソグラフィ工程とドライエッチング工程とイオン注入工程から成る半導体装置の製造法であり、以下の特徴がある。

[0034]

任意のマスクパターンに光強度低減手段を設置可能である為、半導体装置の回路毎にGOLD構造とLDD構造とシングルドレイン構造のトランジスタを簡単に形成することができる。

[0035]

光強度低減手段の透過率と寸法を任意に設定可能である為、フォトリソグラフィエ程とドライエッチング工程を通して形成されるゲート電極の端部に於ける膜厚の薄くなったテーパー形状領域の膜厚と寸法を調整することができる。この為、前記テーパー形状領域のスルードープでイオン注入される低濃度不純物領域(nー領域またはpー領域)の濃度分布とチャネル方向寸法の最適化が可能となり、GOLD構造とLDD構造トランジスタの性能の向上を図ることができる。

[0036]

# 【発明の実施の形態】

# (実施形態1)

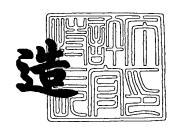

回折格子パターンまたは半透膜から成る光強度低減機能を有するゲート電極形成用フォトマスクまたはレチクルを利用したフォトリソグラフィ工程をGOLD構造多結晶シリコンTFTの形成に適用した場合について、図1~2に基づき記載する。最初に回折格子パターンまたは半透膜から成る光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルの構成について、図1を用いて説明する。

#### [0037]

ゲート電極形成用フォトマスクまたはレチクルに於けるマスクパターンの片側または両側の端部に、マスクパターンからの距離に比例して透過率が徐々に増加する様に構成された光強度低減機能を有する補助パターンを設置する。図1-Aと図1-Bには、この補助パターンの具体例として、解像限界以下のライン/スペースから成る複数のスリット部を有する回折格子パターンの例を示しており、マスクパターンからの距離に比例してスリット幅が徐々に大きくなる構造となっている。尚、このフォトリソグラフィ工程で使用されるレジストはネガ型レジストが適用困難である為、当該ゲート電極形成用フォトマスクまたはレチクル101、105のパターン構成は、ポジ型レジストを前提にしている。よって、ゲー

ト電極形成用マスクパターンの主パターンの領域が遮光部102,106で、光強度低減機能を有する補助パターンの領域がスリット部103,107で、補助パターンの外側の領域が透光部104,108のパターン構成となっている。前記スリット部のスリットの方向は、スリット部103の様に主パターン(遮光部102)の方向と平行でも、スリット部107の様に主パターン(遮光部106)の方向と垂直でも構わない(図1-Aと図1-B)。

# [0038]

前記ゲート電極形成用フォトマスクまたはレチクル101,105に露光光を 照射した場合、遮光部102,106の光強度はゼロであり、透光部104,1 08の光強度は100%である。一方、解像限界以下のライン/スペースから成 る複数のスリット部103,107を有する回折格子パターンで構成される光強 度低減機能を有する補助パターンの光強度は、10~70%の範囲でマスクパターンからの距離に比例して透過率が増加する様に構成されており、その代表的光 強度分布の例を光強度分布109に示す。尚、回折格子パターンに於ける前記スリット部103,107の光強度の調整は、スリット部103,107のピッチ 及びスリット幅の調整により実現している(図1-C)。

### [0039]

次の図1-Dには、補助パターンの具体例として、露光光の光強度を低減する機能を有する半透膜の例を示しており、マスクパターンからの距離に比例して、半透膜の透過率が徐々に増加する様に構成されている。ゲート電極形成用フォトマスクまたはレチクル110に於けるゲート電極形成用マスクパターンの主パターンの領域が遮光部111で、光強度低減機能を有する補助パターンの領域が半透膜から成る半透光部112で、その外側の領域が透光部113である(図1-D)。

#### [0040]

前記ゲート電極形成用フォトマスクまたはレチクル110に露光光を照射した場合、遮光部111及び透光部113の光強度は各々ゼロと100%であり、半透膜から成る半透光部112で構成される補助パターン領域の光強度は、10~70%の範囲でマスクパターンからの距離に比例して透過率が増加する様に構成

されており、その代表的光強度分布の例を光強度分布114に示す(図1-E)

# [0041]

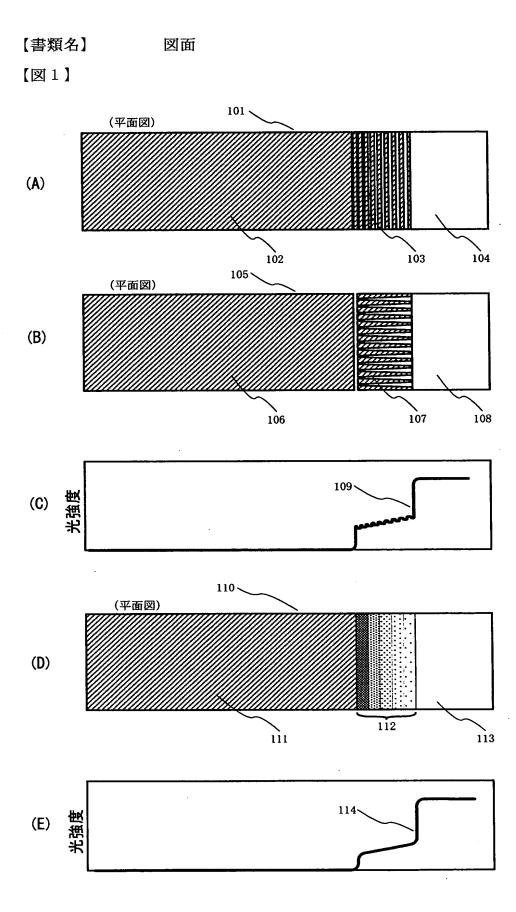

次に回折格子パターンまたは半透膜から成る光強度低減機能を有するゲート電極形成用フォトマスクまたはレチクル101,105,110を利用したGOL D構造多結晶シリコンTFTの形成法について、図2を用いて説明する。

# [0042]

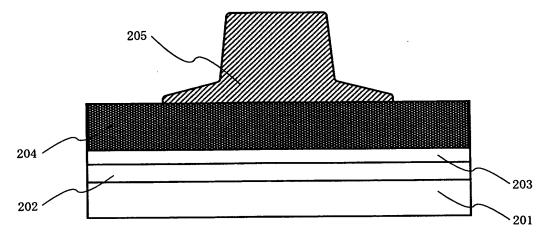

回折格子パターンまたは半透膜から成る光強度低減機能を有する補助パターンを設置した前記ゲート電極形成用フォトマスクまたはレチクル101,105,110をフォトリソグラフィ工程に適用することにより、レジストパターンの両側端部に於ける膜厚が、通常と比較し10~60%の範囲内で薄く形成され、且つ端部に近づく程、レジスト膜厚が徐々に薄くなったテーパー形状領域を有する現像後レジストパターン205が形成される(図2-A)。

# [0043]

尚、前記現像後レジストパターン205のテーパー形状領域のレジスト膜厚は、テーパー形状領域の端部に近づく程、薄くなっており、対応するマスクパターンに設置された前記補助パターン領域の透過率を適宜調整することにより、自由に設定可能である。そして後工程である第1のドライエッチング処理及び第2のドライエッチング処理で形成されるゲート電極のテーパー形状領域のエッチング残膜厚を考慮して、前記現像後レジストパターン205のテーパー形状領域は適切なレジスト膜厚に形成される。また、前記現像後レジストパターン205の前記テーパー形状領域の寸法は、対応するマスクパターンに設置された前記補助パターン領域の寸法を調整することにより、自由に設定可能である。そして現像後レジストパターン205の前記テーパー形状領域は、最終的に形成されるGOLD構造トランジスタに於ける低濃度不純物領域(nー領域)の寸法を考慮して、適切な長さに形成される(図2-A)。

### [0044]

次に、前記現像後レジストパターン205をマスクに、第1のドライエッチング処理を行う。この所定時間のドライエッチング工程に於いて、前記現像後レジ

ストパターン205から露出しているゲート電極膜204は、完全にエッチングされ、更に下層側に存在するゲート絶縁膜203が若干オーバーエッチングされるまで、ドライエッチング処理が行われる。一方、前記現像後レジストパターン205の端部に於けるレジスト膜厚の薄くなったテーパー形状領域では、ゲート電極膜204とレジスト膜との選択比の問題で、レジスト膜が徐々にエッチングされる為、ドライエッチングの途中で、前記テーパー形状領域でのレジストパターン端部のレジスト膜厚の薄い領域から下地のゲート電極膜204が徐々に露出し、当該領域の端部からゲート電極膜204のエッチングが進行することになる。この為、当該領域のゲート電極膜204の残膜厚が初期膜厚の5~30%程度の所定膜厚になる様にドライエッチングした後、ゲート電極端部に近づく程、ゲート電極膜厚の薄くなる構造のテーパー形状領域を有したゲート電極207が形成される。

# [0045]

ここで、第1のドライエッチング工程に於けるレジストパターンの形状は、パターン端部に近づく程、レジスト膜厚の薄くなったテーパー形状領域を有する現像後レジストパターン205から、最終的にはドライエッチング後レジストパターン206の形状に変化している。このドライエッチングにより、ゲート電極端部に近づく程、膜厚の薄くなる構造のテーパー形状領域を有するゲート電極207が形成され、前記ゲート電極207から露出した領域に存在する下層膜であるゲート絶縁膜208は、オーバーエッチングにより、薄くなった形状に変化している(図2-B)。

### [0046]

次に前記ゲート電極207をマスクとして、ソース及びドレイン領域にn型不純物の高濃度イオン注入を行う。ゲート電極207から露出した領域に対応する多結晶シリコン膜202に、ソース及びドレイン領域となる高濃度不純物領域(n+領域)209が形成される。またゲート電極端部に近づく程、ゲート電極膜厚の薄くなる構造の前記テーパー形状領域に対応する多結晶シリコン膜202には、低濃度不純物領域(n-領域)210が形成される。この際、ゲート電極207の端部の前記テーパー形状領域では、ゲート電極207の端部に近づく程、

ゲート電極膜厚が徐々に薄くなる構造となっている為、スルードープでイオン注入される低濃度不純物領域(n - 領域)210の不純物濃度には濃度勾配が存在し、ゲート電極207の端部即ちソース及びドレイン領域の端部に近づく程、徐々に不純物濃度が高くなる傾向を有している(図2-B)。

# [0047]

尚、前記イオン注入に於ける注入条件は、ドーズ量が $5\times10^{14}\sim5\times10^{15}$  atoms/cm $^2$ 及び加速電圧が $60\sim100$  k e Vである。また前記高濃度不純物領域(n+領域)209に於いては $1\times10^{20}\sim1\times10^{22}$ atoms/cm $^3$ 程度の不純物がイオン注入され、前記低濃度不純物領域(n-領域)210に於いては $1\times10^{18}\sim1\times10^{19}$ atoms/cm $^3$ 程度の不純物がイオン注入されている。

# [0048]

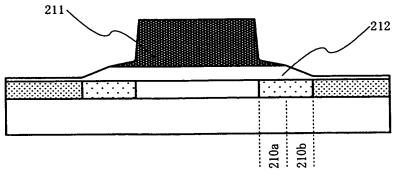

次に前記ゲート電極207をマスクとして、第2のドライエッチング処理を行う。この所定時間のドライエッチング処理により、ゲート電極207の端部のテーパー形状領域はエッチングされ、テーパー形状領域のゲート電極度厚は更に薄くなり、テーパー形状領域の端部は後退する。この結果、ゲート電極207はゲート電極211の形状に変化し、濃度勾配を有した前記低濃度不純物領域(nー領域)210は、ゲート電極211とオーバーラップしているLov領域210aとオーバーラップしてないLoff領域210bに区分される。この際、ドライエッチング処理条件を適宜変更することにより、ゲート電極207の前記テーパー形状領域の範囲内で、ゲート電極211の寸法を自由に調整することができる。即ち、ゲート電極207の前記テーパー形状領域の範囲内で、Lov領域210aの寸法とLoff領域210bの寸法を自由に調整することができる。また、ゲート電極211から露出した下地のゲート絶縁膜212は、ドライエッチングにより更に薄くなっている。この後、ゲート電極211のドライエッチングマスクである不要なレジストパターン206は、除去される(図2-C)。

### [0049]

尚、ここではGOLD構造多結晶シリコンTFTの形成法について記載したが、光強度低減機能を有する補助パターンを設置した前記ゲート電極形成用フォトマスクまたはレチクル101,105,110は、シリコン基板等の半導体基板

を使用するGOLD構造MOS型トランジスタの形成にも、勿論適用可能である。この場合は、高濃度不純物領域(n+領域)と低濃度不純物領域(nー領域)は、シリコン基板等の半導体基板に形成される。

[0050]

# (実施形態2)

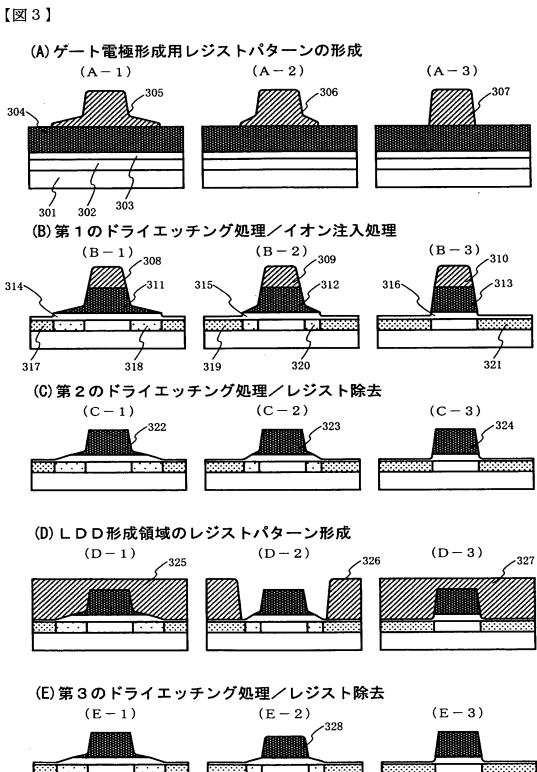

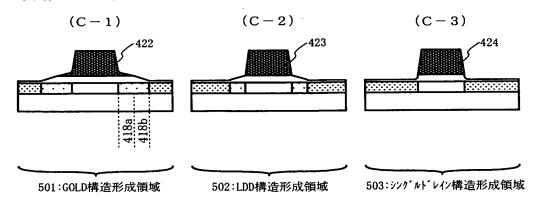

液晶ディスプレイ等の半導体装置には様々な回路が内包されており、回路によってはホットキャリア対策効果に優れたGOLD構造が適している場合もあれば、オフ電流値の小さいLDD構造が適している場合もあり、場合によっては、シングルドレイン構造が適している場合もある。従って、回路毎にGOLD構造とLDD構造とシングルドレイン構造の多結晶シリコンTFTを別々に形成する必要がある。実施形態2に於いては、回路毎にGOLD構造とLDD構造とシングルドレイン構造の多結晶シリコンTFTを別々に形成する方法について、図3に基づき記載する。

# [0051]

尚、本実施形態では、第2のドライエッチング処理後に於けるLDD構造形成領域502のゲート電極323にエッチング残膜であるテーパー形状領域が残存している場合について例示しており、次工程のLDD構造形成領域502のみを開口する為のレジストパターン形成と第3のドライエッチング処理が必要な場合について記載している。また、前記ゲート電極形成用フォトマスクまたはレチクル101,105,110(図1-A,B,D)の構成については、既に実施形態1に記載している為、ここでは割愛する。

#### [0052]

本実施形態で使用する基板構造は、ガラス基板301上に所定膜厚の多結晶シリコン膜302と所定膜厚のゲート絶縁膜303と所定膜厚のゲート電極膜304が各々積層されている構造の基板を使用する。前記構造の基板上に、回折格子パターンまたは半透膜から成る光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクル101,105,110(図1-A,B,D)を適用したフォトリソグラフィ工程を行い、現像後レジストパターン305,306,307を形成する。

# [0053]

この際、適用する前記ゲート電極形成用フォトマスクまたはレチクル101,105,110に於いて、GOLD構造形成領域501とLDD構造形成領域502に対応するゲート電極形成用マスクパターンには光強度低減機能を有する補助パターンを設置し、シングルドレイン構造形成領域503に対応するゲート電極形成用マスクパターンには前記補助パターンを設置しないパターン構成とする。この結果、GOLD構造形成領域501とLDD構造形成領域502の現像後レジストパターン305,306には、端部に近づく程、レジスト膜厚の徐々に薄くなるテーパー形状領域が形成され、シングルドレイン構造形成領域503の現像後レジストパターン307には前記テーパー形状領域が存在せず、矩形形状の現像後レジストパターン307が形成される(図3-A)。

#### [0054]

尚、GOLD構造形成領域501とLDD構造形成領域502に於ける現像後レジストパターン305,306の前記テーパー形状領域のレジスト膜厚は、テーパー形状領域の端部に近づく程、薄くなっており、各々対応するマスクパターンに設置された前記補助パターン領域の透過率を適宜調整することにより、自由に設定可能である。そして後工程である第1のドライエッチング処理及び第2のドライエッチング処理で形成されるゲート電極のテーパー形状領域のエッチング残膜厚を考慮して、現像後レジストパターン305,306の前記テーパー形状領域は適切なレジスト膜厚に形成される。また、GOLD構造形成領域501とLDD構造形成領域502に於ける現像後レジストパターン305,306の前記テーパー形状領域の寸法は、各々対応するマスクパターンに設置された前記補助パターン領域の寸法を調整することにより、自由に設定可能である。そして現像後レジストパターン305,306の前記テーパー形状領域は、最終的に形成されるGOLD構造とLDD構造トランジスタに於ける各低濃度不純物領域(nー領域)の寸法を考慮して、適切な長さに形成される。

### [0055]

本実施形態では、GOLD構造形成領域501とLDD構造形成領域502に 於ける現像後レジストパターン305,306のテーパー形状領域のレジスト膜 厚が同等で、且つGOLD構造形成領域501の現像後レジストパターン305 の場合と比較し、LDD構造形成領域502の現像後レジストパターン306に 於けるテーパー形状領域が寸法的に小さい場合を例示している(図3-A)。

# [0056]

次に、第1のドライエッチング処理を行う。この所定時間のドライエッチング 処理により、GOLD構造形成領域501とLDD構造形成領域502に於いて は、ゲート電極端部に近づく程、ゲート電極膜厚の薄くなる構造のテーパー形状 領域を有したゲート電極311,312が形成される。この際、ゲート電極311,312のテーパー形状領域の残膜厚は、初期膜厚の5~30%程度の所定膜 厚になる様にドライエッチング処理される。一方のシングルドレイン構造形成領域503に於いては、矩形形状のゲート電極313が形成される。尚、ドライエッチングのマスクとなったレジストパターンは、現像後レジストパターン305,306,307の形状から各々ドライエッチング後レジストパターン308,309,310の形状に変化している。また、ゲート電極311,312,313から露出した領域のゲート絶縁膜の形状は、エッチングにより薄くなっており、各々ゲート絶縁膜314,315,316の形状に変化している(図3-B)

# [0057]

次に、前記ゲート電極311,312,313をマスクに n型不純物の高濃度イオン注入を行う。GOLD構造形成領域501とLDD構造形成領域502に於いては、ゲート電極311,312の外側に対応する多結晶シリコン膜302にソース及びドレイン領域となる高濃度不純物領域(n+領域)317,319が形成され、ゲート電極膜厚の薄い前記テーパー形状領域に対応する多結晶シリコン膜302に低濃度不純物領域(n-領域)318,320が形成される。シングルドレイン構造形成領域503に於いては、ゲート電極313の外側に対応する多結晶シリコン膜302にソース及びドレイン領域となる高濃度不純物領域(n+領域)321のみが形成される(図3-B)。

#### [0058]

次に、第2のドライエッチング処理を行う。この所定時間のドライエッチング

処理により、GOLD構造形成領域501に於いては、ゲート電極311の端部の前記テーパー形状領域がドライエッチングされ、テーパー形状領域のゲート電極度厚は更に薄くなり、テーパー形状領域の端部であるゲート電極311の端部は後退し、ゲート電極322が形成される。そして前記低濃度不純物領域(nー領域)318は、ゲート電極322とオーバーラップしているLov領域318aとオーバーラップしていないLoff領域318bに区分される。LDD構造形成領域502に於けるゲート電極312の前記テーパー形状領域も、GOLD構造形成領域501の場合と同様にドライエッチングされ、エッチング残膜であるテーパー形状領域を有するゲート電極323が形成される。これに対し、シングルドレイン構造形成領域503のゲート電極313が形成される。これに対し、シングルドレイン構造形成領域503のゲート電極313が形成されるが、当該ゲート電極313が矩形形状である為、下地のゲート絶縁膜316が更にエッチングされ、薄くなるだけである。この後、ゲート電極322,323,324のドライエッチングマスクである不要なレジストパターンは、除去される(図3-C)。

# [0059]

次に、LDD構造形成領域502に於けるゲート電極323のエッチング残膜である前記テーパー形状領域が残存している為、前記テーパー形状領域を選択的に除去する必要がある。よって、LDD構造形成領域502のみを開口する様に、新規にレジストパターン325~327を形成する(図3-D)。

### [0060]

次に、第3のドライエッチング処理を行う。この所定時間のドライエッチング処理により、LDD構造形成領域502に於けるゲート電極323の前記テーパー形状領域は選択的にエッチング除去され、矩形形状のゲート電極328が形成される。この結果、多結晶シリコン膜に形成された低濃度不純物領域(n-領域)320とゲート電極328はオーバーラップしない構造となり、LDD構造トランジスタが形成される。この後、ドライエッチングマスクである前記レジストパターン325~327は、除去される(図3-E)。

#### [0061]

尚、ここではGOLD構造とLDD構造とシングルドレイン構造の多結晶シリ

コンTFTの形成法について記載したが、光強度低減機能を有する補助パターンを設置した前記ゲート電極形成用フォトマスクまたはレチクル101,105,110は、シリコン基板等の半導体基板を使用する同構造のMOS型トランジスタの形成にも、勿論適用可能である。この場合は、高濃度不純物領域(n+領域)と低濃度不純物領域(nー領域)は、シリコン基板等の半導体基板に形成される。

#### [0062]

以上の製造工程により、回路毎にGOLD構造とLDD構造とシングルドレイン構造の薄膜トランジスタを別々に形成することができる。

# [0063]

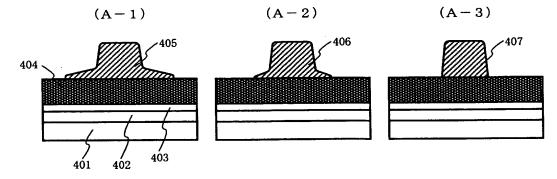

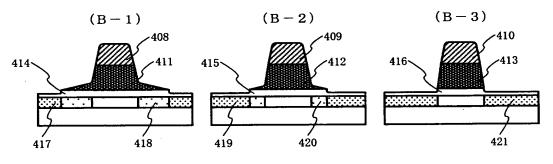

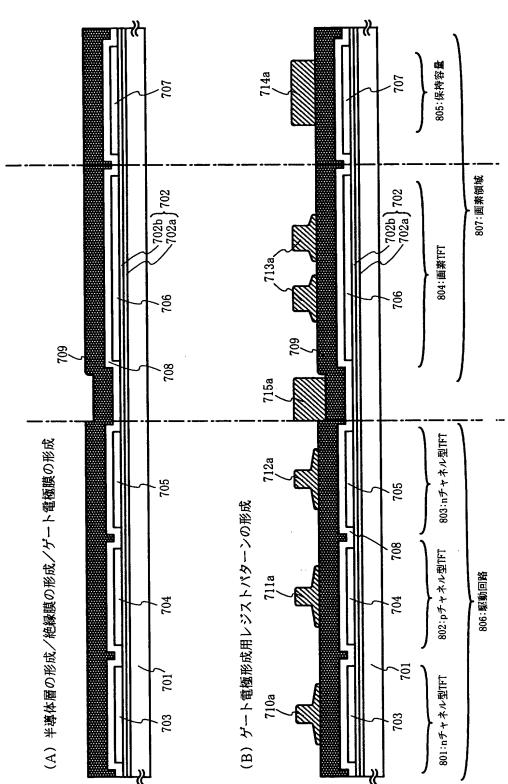

# (実施形態3)

実施形態3では、回路毎にGOLD構造とLDD構造とシングルドレイン構造の薄膜トランジスタを別々に形成する方法に於いて、LDD構造形成領域502のみを開口する為のレジストパターン形成と第3のドライエッチング処理が不要な工程簡略化プロセスについて、図4に基づき記載する。

#### [0064]

本実施形態で使用する基板構造は、ガラス基板401上に所定膜厚の多結晶シリコン膜402と所定膜厚のゲート絶縁膜403と所定膜厚のゲート電極膜404が各々積層されている構造の基板を使用する。前記構造の基板上に、回折格子パターンまたは半透膜から成る光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクル101,105,110(図1-A,B,D)を適用したフォトリソグラフィ工程を行い、現像後レジストパターン405,406,407を形成する。

#### [0065]

この際、適用する前記ゲート電極形成用フォトマスクまたはレチクル101, 105,110に於いて、GOLD構造形成領域501とLDD構造形成領域5 02に対応するゲート電極形成用マスクパターンには光強度低減機能を有する補助パターンを設置し、シングルドレイン構造形成領域503に対応するゲート電極形成用マスクパターンには前記補助パターンを設置しないパターン構成とする 。この結果、GOLD構造形成領域501とLDD構造形成領域502の現像後レジストパターン405,406には、端部に近づく程、レジスト膜厚の徐々に薄くなったテーパー形状領域が形成され、シングルドレイン構造形成領域503の現像後レジストパターン407には前記テーパー形状領域が存在せず、矩形形状の現像後レジストパターン407が形成される(図4-A)。

# [0066]

本実施形態では、第2のドライエッチング処理後に於いて、LDD構造形成領域502の当該ゲート電極にエッチング残膜であるテーパー形状領域が残存しない様にする為、GOLD構造形成領域501に於ける現像後レジストパターン405と比較し、LDD構造形成領域502に於ける現像後レジストパターン406のテーパー形状領域のレジスト膜厚が相対的に薄くなる様に構成されている(図4-A)。

# [0067]

次に、第1のドライエッチング処理を行う。この所定時間のドライエッチング 処理により、GOLD構造形成領域501とLDD構造形成領域502に於いて は、ゲート電極端部に近づく程、ゲート電極膜厚の薄くなる構造のテーパー形状 領域を有したゲート電極411,412が形成される。この際、GOLD構造形 成領域501とLDD構造形成領域502のゲート電極411,412に於けるテーパー形状領域の残膜厚は、初期膜厚の5~30%程度の所定膜厚になる様に ドライエッチング処理されており、またゲート電極412に於けるテーパー形状 領域の残膜厚は、ゲート電極411に比べ、相対的に薄くなっている。一方のシングルドレイン構造形成領域503に於いては、矩形形状のゲート電極413が 形成される。尚、ドライエッチングのマスクとなったレジストパターンは、現像後レジストパターン405,406,407の形状から各々ドライエッチング後レジストパターン405,406,407の形状に変化している。また、ゲート電極411,412,413から露出した領域のゲート絶縁膜の形状は、エッチングにより薄くなっており、各々ゲート絶縁膜414,415,416の形状に変化している(図4-B)。

[0068]

次に、前記ゲート電極4 1 1, 4 1 2, 4 1 3 をマスクに n型不純物の高濃度 イオン注入を行う。GOLD構造形成領域5 0 1 とLDD構造形成領域5 0 2 に 於いては、ゲート電極4 1 1, 4 1 2 の外側に対応する多結晶シリコン膜4 0 2 にソース及びドレイン領域となる高濃度不純物領域(n+領域)4 1 7, 4 1 9 が形成され、ゲート電極膜厚の薄い前記テーパー形状領域に対応する多結晶シリコン膜4 0 2 に低濃度不純物領域(n - 領域)4 1 8, 4 2 0 が形成される。シングルドレイン構造形成領域5 0 3 に於いては、ゲート電極4 1 3 の外側に対応する多結晶シリコン膜4 0 2 にソース及びドレイン領域となる高濃度不純物領域(n+領域)4 2 1 のみが形成される(図4 - B)。

[0069]

次に、第2のドライエッチング処理を行う。この所定時間のドライエッチング 処理により、GOLD構造形成領域501に於いては、ゲート電極411の端部 の前記テーパー形状領域がドライエッチングされ、テーパー形状領域のゲート電 極膜厚は更に薄くなり、テーパー形状領域の端部であるゲート電極411の端部 は後退し、ゲート電極422が形成される。そして前記低濃度不純物領域(n-領域)418は、ゲート電極422とオーバーラップしているLov領域418a とオーバーラップしていないLoff領域418bに区分される。またLDD構造 形成領域502の場合、第1のドライエッチング処理後に於いて、ゲート電極4 12のテーパー形状領域の残膜厚が相対的に薄い為、第2のドライエッチング処 理により、前記テーパー形状領域は完全にエッチング除去され、矩形形状のゲー ト電極423が形成される。このゲート電極423は前記低濃度不純物領域(n - 領域)420とオーバーラップしない構造となっており、LDD構造トランジ スタが形成される。これに対し、シングルドレイン構造形成領域503のゲート 電極413も同様にドライエッチング処理が行われ、ゲート電極424が形成さ れるが、ゲート電極413が矩形形状である為、下地のゲート絶縁膜416が更 にエッチングされ、薄くなるだけである。この後、ゲート電極422,423, 424のドライエッチングマスクであるレジストパターンは、除去される(図4 -C) .

[0070]

以上の工程簡略化した製造工程により、回路毎にGOLD構造とLDD構造とシングルドレイン構造の薄膜トランジスタを別々に形成することができる。

# [0071]

上記の実施形態 1 ~ 3 で説明した本発明について、以下に記載する実施例で更なる詳細な説明を行うこととする。

[0072]

# 【実施例】

#### (実施例1)

回折格子パターンまたは半透膜から成る光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクル101,105,110(図1-A,B,D)をゲート電極形成用のフォトリソグラフィ工程に適用し、GOLD構造とLDD構造の多結晶シリコンTFTで構成されるアクティブマトリクス型液晶ディスプレイの製造法について、図5~10を用いて詳細に説明する。

# [0073]

最初に、液晶ディスプレイ全体の回路構成を図5に示す。液晶ディスプレイは、画素領域601と画素領域601を駆動する為の周辺回路で構成されている。周辺回路は、シフトレジスタ回路602,606とレベルシフタ回路603,607とバッファ回路604,608とサンプリング回路605で構成されている。周辺回路であるシフトレジスタ回路602,606とレベルシフタ回路603,607とバッファ回路604,608には、ホットキャリア対策効果に優れたGOLD構造の多結晶シリコンTFTが使われており、一方、画素領域601と周辺回路の一部であるサンプリング回路605にはオフ電流値を抑える効果に優れたLDD構造の多結晶シリコンTFTが使われている(図5)。

#### [0074]

前記回路構成の液晶ディスプレイの製造法について、以下に図6~10を用いて具体的に記載する。

#### [0075]

尚、本実施例では、第2のドライエッチング処理後に於いて、LDD構造形成領域のゲート電極735(図7-B)にエッチング残膜であるテーパー形状領域

が残存している場合について例示しており、次工程のLDD構造形成領域のみを 開口する為のレジストパターン形成と第3のドライエッチング処理が必要な場合 について記載している。

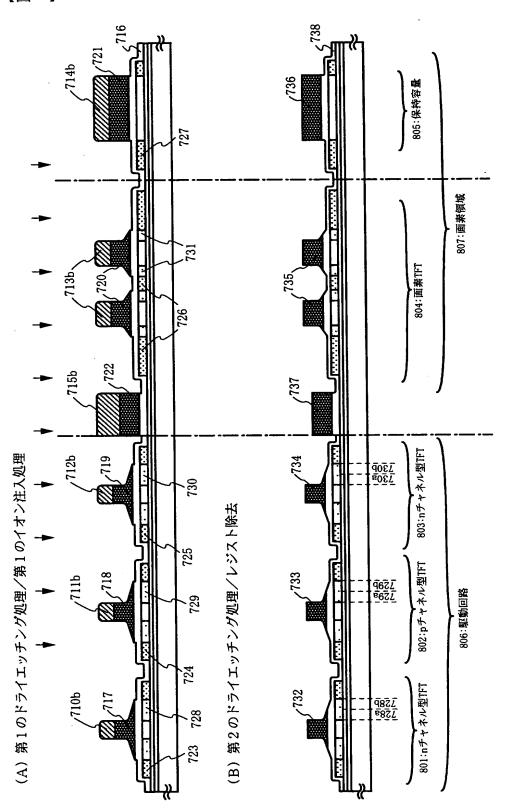

# [0076]

最初に、ガラス基板701上にプラズマСVD法により、各々組成比の異なる 第1層目の酸化窒化シリコン膜702aを50nmと第2層目の酸化窒化シリコ ン膜702bを100nmの膜厚で堆積し、下地膜702を成膜する。尚、ここ で用いるガラス基板701としては、石英ガラスまたはバリウムホウケイ酸ガラ スまたはアルミノホウケイ酸ガラス等が有る。次に前記下地膜702 (702 a と702b)上にプラズマCVD法により、非晶質シリコン膜55nmを堆積し た後、ニッケル含有溶液を非晶質シリコン膜上に保持させた。この非晶質シリコ ン膜を脱水素化処理(500℃−1時間)した後、熱結晶化(550℃−4時間 )を行い、更にレーザーアニール処理により多結晶シリコン膜とした。次にフォ トリソグラフィ工程及びエッチング工程により、この多結晶シリコン膜をパター ニングし、半導体層703~707を形成した。この際、半導体層703~70 7の形成後に、TFTのVthを制御する為の不純物元素(ボロンまたはリン) のドーピングを実施しても構わない。次に半導体層703~707を覆う様に、 プラズマCVD法により110nm厚の酸化窒化シリコン膜から成るゲート絶縁 膜708を形成し、更にゲート絶縁膜708上に400nm厚のTaN膜から成 るゲート電極膜709をスパッタ法により堆積した(図6-A)。

#### [0077]

次に、露光光の光強度を低減する機能を有するライン/スペースから成る回折格子パターンまたは半透膜で構成される補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用し、現像後レジストパターン710a~715aを形成する(図6-B)。

### [0078]

この際、駆動回路806の領域はGOLD構造形成領域に該当し、画素領域807での画素TFT804の領域はLDD構造形成領域に該当する為、適用する前記ゲート電極形成用フォトマスクまたはレチクルに於いて、対応するマスクパ

ターンには光強度低減機能を有する補助パターンが設置される。また、画素領域 807の領域に於いて、単なる電極として機能する電極パターンに対応するマス クパターンには、補助パターンを設置する必要がない為、前記補助パターンが設 置されないパターン構成となっている。この結果、GOLD構造形成領域の現像 後レジストパターン710a~712a及びLDD構造形成領域の現像後レジス トパターン713aには、端部に近づく程、レジスト膜厚の徐々に薄くなるテー パー形状領域が形成される。尚、GOLD構造形成領域の現像後レジストパター ン 7 1 0 a ~ 7 1 2 a 及び L D D 構造形成領域の現像後 レジストパターン 7 1 3 aに於ける前記テーパー形状領域の寸法は、最終的に形成されるGOLD構造及 びLDD構造トランジスタに於ける低濃度不純物領域(n-領域)の寸法を考慮 し、当該マスクパターンの前記補助パターン領域の寸法を調整することにより、 適切な長さに形成される。本実施例では、GOLD構造形成領域の現像後レジス トパターン710a~712aと比較し、LDD構造形成領域の現像後レジスト パターン713aに於ける前記テーパー形状領域の寸法が小さい場合について例 示した。一方の現像後レジストパターン714a~715aは単なる電極を形成 する為のレジストパターンである為、前記テーパー形状領域は存在せず、矩形形 状のレジストパターンが形成される(図6-B)。

# [0079]

次に前記現像後レジストパターン710a~715aをマスクに、第1のドライエッチング処理を行う。この所定時間のドライエッチング処理により、GOL D構造形成領域の現像後レジストパターン710a~712a及びLDD構造形成領域の現像後レジストパターン713aをマスクとしてエッチングした結果、ゲート電極端部に近づく程、ゲート電極膜厚の薄くなる構造のテーパー形状領域を有したゲート電極717~720が形成される。この際、ゲート電極717~720のテーパー形状領域の残膜厚は、初期膜厚400nmの5~30%程度(好ましくは7~8%程度、30nm程度)になる様にエッチング処理される。一方の矩形形状の現像後レジストパターン714a~715aをマスクとしてドライエッチングした結果、矩形形状の電極721~722が形成される。尚、ドライエッチング工程に於けるレジストパターンの形状は、現像後レジストパターン

710a~715aからドライエッチング後レジストパターン710b~715bの形状に変化している。また、ゲート電極717~720及び電極721~722から露出した領域の酸化窒化シリコン膜から成るゲート絶縁膜708は、ドライエッチングにより薄くなった形状のゲート絶縁膜716に変化している(図7-A)。

# [0080]

次に、ゲート電極717~720及び電極721~722をマスクに、第1の イオン注入処理であるn型不純物の高濃度イオン注入を行う。半導体層703~ 705に於いて、GOLD構造形成領域のゲート電極717~719の外側に対 応する領域にソース及びドレイン領域となる高濃度不純物領域(n+領域)72 3 ~ 7 2 5 が形成され、ゲート電極膜厚の薄い前記テーパー形状領域に対応する 領域には、低濃度不純物領域(nー領域)728~730が形成される。また、 半導体層706に於いて、LDD構造形成領域のゲート電極720の外側に対応 する領域にソース及びドレイン領域となる高濃度不純物領域(n+領域)726 が形成され、ゲート電極膜厚の薄い前記テーパー形状領域に対応する領域には、 低濃度不純物領域(n-領域)731が形成される。一方、保持容量805の領 域である半導体層707に於いて、電極721の外側に対応する領域には高濃度 不純物領域(n+領域)727のみが形成される。この際、イオン注入条件はn 型不純物としてリン(P)を用い、ドーズ量が $5 \times 10^{14} \sim 5 \times 10^{15}$ atoms/cm  $^2$ 及び加速電圧が60~100keVの条件で処理した。また注入される実際の 不純物濃度は、高濃度不純物領域(n+領域)723~726で1×10<sup>20</sup>~1 × 10<sup>22</sup>atoms/cm<sup>3</sup>程度、低濃度不純物領域(n - 領域) 728~731で1×  $10^{18} \sim 1 \times 10^{19} \text{atoms/cm}^3$ 程度である(図7-A)。

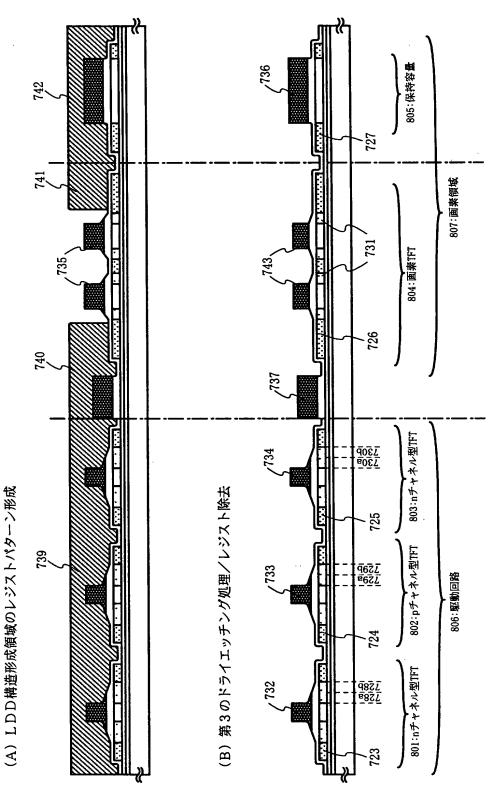

### [0081]

次に、第2のドライエッチング処理を行う。この所定時間のドライエッチング 処理により、GOLD構造形成領域に於けるゲート電極717~719の端部の 前記テーパー形状領域はエッチングされ、テーパー形状領域のエッチング残膜厚 は更に薄くなり、テーパー形状領域の端部は後退し、ゲート電極732~734 が形成される。そして前記低濃度不純物領域(n-領域)728~730は、ゲ ート電極732~734とオーバーラップしているLov領域728a~730aとオーバーラップしていないLoff領域728b~730bに区分される。LDD構造形成領域に於けるゲート電極720の前記テーパー形状領域も、GOLD構造形成領域の場合と同様にドライエッチングされ、エッチング残膜であるテーパー形状領域を有するゲート電極735が形成される。一方の矩形形状の電極721~722も同様にドライエッチング処理が行われ、電極736~737が形成されるが、電極の形状に大きな変化は認められない。この後、ゲート電極732~735及び電極736~737のドライエッチングマスクである不要なレジストパターンは、除去される(図7-B)。

# [0082]

次に、LDD構造形成領域に於ける前記ゲート電極735のエッチング残膜であるテーパー形状領域が残存している為、前記テーパー形状領域を選択的に除去する必要がある。この為、LDD構造形成領域のみを開口する様に、新規にレジストパターン739~742を形成する(図8-A)。

# [0083]

次に、第3のドライエッチング処理を行う。この所定時間のドライエッチング処理により、LDD構造形成領域に於けるゲート電極735の前記テーパー形状領域は選択的にエッチング除去され、矩形形状のゲート電極743が形成される。この結果、半導体層706に形成された低濃度不純物領域(n-領域)731とゲート電極743はオーバーラップしない構造となり、LDD構造トランジスタが形成される。この後、ドライエッチングマスクである前記レジストパターン739~742は、除去される(図8-B)。

#### [0084]

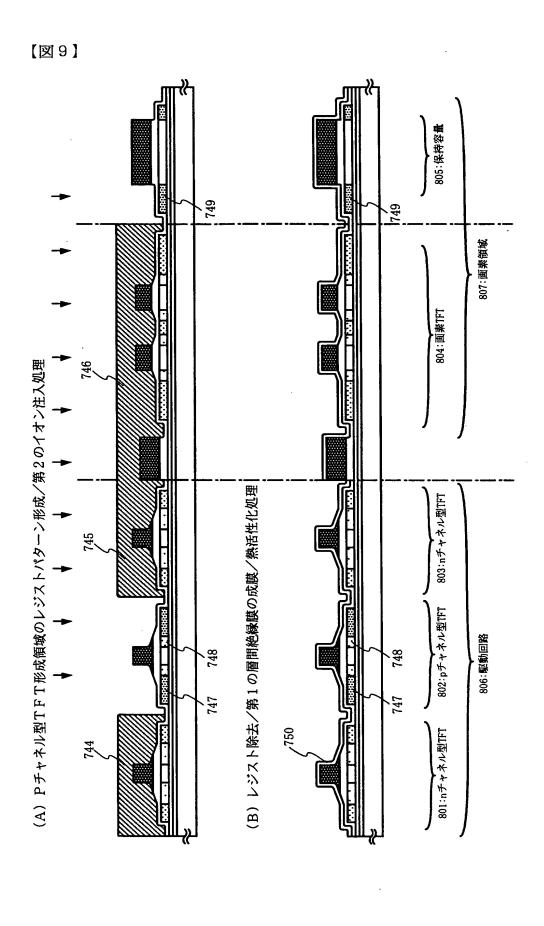

次に、駆動回路806に於けるpチャネル型TFT802の領域と画素領域807に於ける保持容量805の領域をレジスト開口させる為の新規のフォトリソグラフィ処理をおこない、レジストパターン744~746を形成する(図9-A)。

# [0085]

前記レジストパターン744~746をマスクに、第2のイオン注入処理であ

るp型不純物の高濃度イオン注入を行う。この際、pチャネル型TFT802の 領域には、ゲート電極733をマスクに前記一導電型とは逆の導電型を付与する 不純物元素のp型不純物であるボロン(B)等がイオン注入される。そして半導 体層704に於いて、ゲート電極733の外側に対応する領域にソース及びドレ イン領域となる高濃度不純物領域(p+領域)747が形成され、ゲート電極7 3 3 の端部のゲート電極膜厚が薄くなったテーパー形状領域に対応する領域に低 濃度不純物領域 (p-領域) 748が形成される。第2のイオン注入領域には、 第1のイオン注入により、n型不純物であるリン(P)が既にイオン注入されて いるが、 p型不純物であるボロン(B)の濃度が $2 \times 10^{20} \sim 2 \times 10^{21}$ atoms/ cm<sup>3</sup>となる様に高濃度にイオン注入される為、 p チャネル型TFT802のソー ス及びドレイン領域として機能することができる。尚、保持容量805の形成領 域である半導体層707に於いても、電極736の外側に対応する領域に高濃度 不純物領域 (p+領域) 749が形成され、構造的にはシングルドレイン構造の p チャネル型多結晶シリコンTFTと同様の構造が形成されるが、保持容量80 5として機能する領域である為、シングルドレイン構造多結晶シリコンTFTに はなっていない(図9-A)。

# [0086]

次に前記レジストパターン744~746を除去した後、プラズマCVD法により150mm厚の酸化窒化シリコン膜から成る第1の層間絶縁膜750を堆積させる。更に、半導体層703~707に注入された不純物元素(n型不純物とp型不純物)を熱活性化処理する為、550℃-4時間の熱アニール処理を行う。尚、本実施例では、不純物元素の熱活性化処理と同時に、オフ電流値の低下と電界効果移動度の向上を目的として、半導体層703~707を結晶化する際に使用した触媒のニッケル(Ni)を不純物領域723~727に含まれている高濃度のリン(P)でゲッタリングしている。このゲッタリング処理により、チャネル形成領域となる半導体層中のニッケル(Ni)濃度の低減を達成している。この方法で製造したチャネル形成領域を有する多結晶シリコンTFTは、結晶性が良好な為、高い電界効果移動度を有し、オフ電流値の低下等の良好な電気特性を示すことができる。前記熱活性化処理は、第1の層間絶縁膜750を堆積する

前に行っても構わないが、ゲート電極 $732\sim734$ , 743と電極 $736\sim737$ 00配線材料の耐熱性が弱い場合には、本実施例の様に、層間絶縁膜を堆積した後に熱活性化処理を行う方が望ましい。次に水素を3%含有する窒素雰囲気中で410 $\mathbb{C}-1$ 時間の水素化処理を行うことにより、半導体層 $703\sim707$ のダングリングボンドを終端させる(図9-B)。

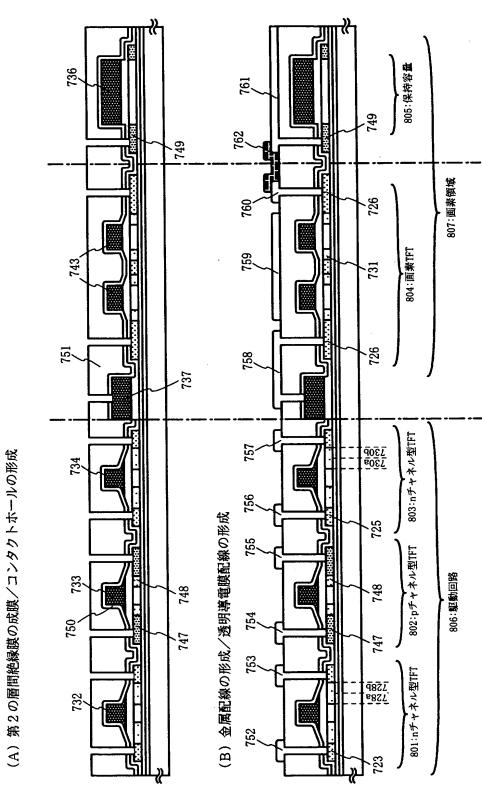

# [0087]

次に酸化窒化シリコン膜から成る第1の層間絶縁膜750の上に、1.6 $\mu$ m 厚のアクリル樹脂膜から成る有機絶縁材料の第2の層間絶縁膜751を成膜する。その後、フォトリソグラフィ処理とドライエッチング処理により、第2の層間絶縁膜751にコンタクトホールを形成する。この際、このコンタクトホールは、ソース配線として機能する電極737と不純物領域723,725,726,747,749に接続する様に形成される(図10-A)。

# [0088]

次に、駆動回路806の不純物領域723,725,747と電気的に接続する為の金属配線752~757を形成する。また前記金属配線752~757と同時に、画素領域807の接続電極758,760,761とゲート配線759を形成する。尚、金属配線材料は、50nm厚のTi膜と500nm厚のA1-Ti合金膜の積層膜で構成されている。接続電極758は、不純物領域726を介して、ソース配線として機能する電極737と画素TFT804を電気的に接続する為に形成されている。接続電極760は、画素TFT804の不純物領域726と電気的に接続されており、接続電極761は保持容量805の不純物領域749と電気的に接続されている。ゲート配線759は、画素TFT804の複数のゲート電極743を電気的に接続する為に形成されている。次に、ITO(Indium-Ti-Oxide)等の透明導電膜を80~120nmの厚さで堆積し、フォトリソグラフィ処理とエッチング処理により、画素電極762を形成する。画素電極762は、接続電極760を介して、画素TFT804のソースドレイン領域である不純物領域726と電気的に接続されており、更に接続電極761を介して、保持容量805の不純物領域749と電気的に接続される(図10-B)

[0089]

以上の製造工程により、nチャネル型TFT801とpチャネル型TFT802とnチャネル型TFT803を含有している駆動回路806と、画素TFT804と保持容量805を含有している画素領域807で構成される液晶ディスプレイを製造することができる。

[0090]

(実施例2)

本発明は、様々な半導体表示装置(アクティブマトリクス型液晶表示装置,アクティブマトリクス型EL表示装置,アクティブマトリクス型EC表示装置)に適用することができる。従って、本発明は、前記半導体表示装置を表示媒体として組み込んだ電子機器全般に適用可能である。

[0091]

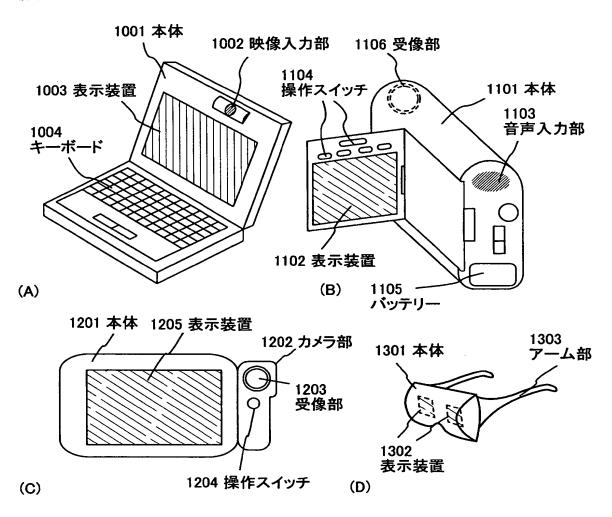

前記電子機器としては、ビデオカメラとデジタルカメラとプロジェクター(リア型またはフロント型)とヘッドマウントディスプレイ(ゴーグル型ディスプレイ)とゲーム機とカーナビゲーションとパーソナルコンピュータと携帯情報端末(モバイルコンピュータ,携帯電話,電子書籍等)等が挙げられ、それらの具体例を図11~13に示す。

[0092]

図11-Aは、本体1001と映像入力部1002と表示装置1003とキーボード1004で構成されたパーソナルコンピューターである。本発明を表示装置1003及び他の回路に適用することができる。

[0093]

図11-Bはビデオカメラであり、本体1101と表示装置1102と音声入力部1103と操作スイッチ1104とバッテリー1105と受像部1106で構成される。本発明を表示装置1102及び他の回路に適用することができる。

[0094]

図11-Cはモバイルコンピュータ (モービルコンピュータ) であり、本体1201とカメラ部1202と受像部1203と操作スイッチ1204と表示装置1205で構成される。本発明を表示装置1205及び他の回路に適用すること

ができる。

[0095]

図11-Dはゴーグル型ディスプレイであり、本体1301と表示装置130 2とアーム部1303で構成される。本発明を表示装置1302及び他の回路に 適用することができる。

[0096]

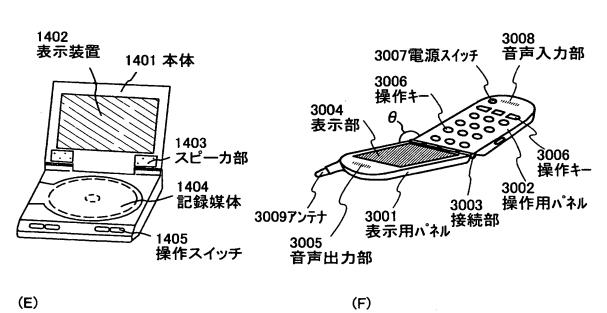

図11-Eはプログラムを記録した記録媒体(以下、記録媒体と略記)を用いるプレーヤーであり、本体1401と表示装置1402とスピーカー部1403と記録媒体1404と操作スイッチ1405で構成される。尚、この装置は記録媒体としてDVD及びCD等が用いられ、音楽鑑賞またはゲームまたはインターネットに利用可能である。本発明を表示装置1402及び他の回路に適用することができる。

[0097]

図11-Fは携帯電話であり、表示用パネル3001と操作用パネル3002と接続部3003と表示部3004と音声出力部3005と操作キー3006と電源スイッチ3007と音声入力部3008とアンテナ3009で構成される。表示用パネル3001と操作用パネル3002は、接続部3003で接続されている。表示用パネル3001の表示部3004が設置されている面と操作用パネル3002の操作キー3006が設置されている面との角度θは、接続部3003に於いて任意に変えることができる。本発明を表示部3004に適用することができる。

[0098]

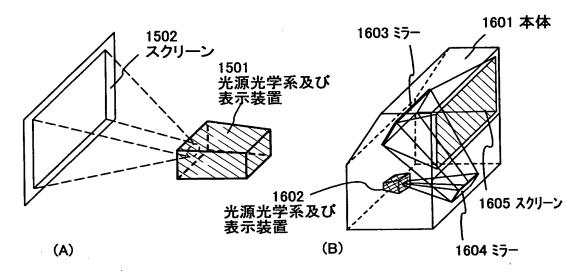

図12-Aはフロント型プロジェクターであり、光源光学系及び表示装置15 01とスクリーン1502で構成される。本発明を表示装置1501及び他の回 路に適用することができる。

[0099]

図12-Bはリア型プロジェクターであり、本体1601と光源光学系及び表示装置1602とミラー1603とミラー1604とスクリーン1605で構成される。本発明を表示装置1602及び他の回路に適用することができる。

# [0100]

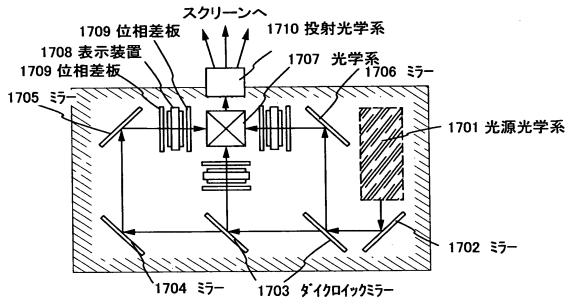

尚、図12-Cは、図12-Aの光源光学系及び表示装置1501と図12-Bの光源光学系及び表示装置1602に於ける構造の一例を示した図である。光源光学系及び表示装置1501,1602は、光源光学系1701とミラー1702,1704~1706とダイクロイックミラー1703と光学系1707と表示装置1708と位相差板1709と投射光学系1710で構成される。投射光学系1710は、投射レンズを備えた複数の光学レンズで構成される。この構成は、表示装置1708を3個使用している為、三板式と呼ばれている。また同図の矢印で示した光路に於いて、実施者は光学レンズ及び偏光機能を有するフィルムまたは位相差を調整する為のフィルムまたはIRフィルム等を適宜に設けても良い。

# [0101]

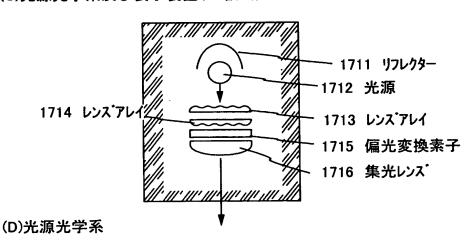

また図12-Dは、図12-Cに於ける光源光学系1701の構造の一例を示した図である。本実施例に於いては、光源光学系1701はリフレクター1711と光源1712とレンズアレイ1713~1714と偏光変換素子1715と集光レンズ1716で構成される。尚、同図に示した光源光学系は一例であり、この構成に限定されない。例えば、実施者は光源光学系に光学レンズ及び偏光機能を有するフィルムまたは位相差を調整するフィルムまたはIRフィルム等を適宜に設けても良い。

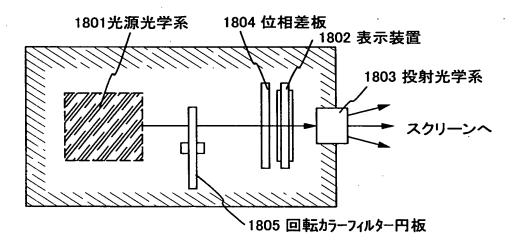

#### [0102]

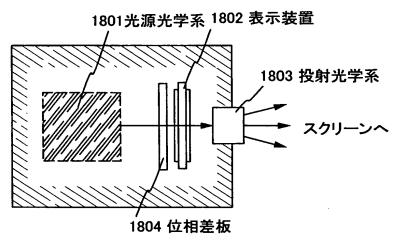

次の図13-Aは、単板式の例を示したものである。同図に示した光源光学系及び表示装置は、光源光学系1801と表示装置1802と投射光学系1803と位相差板1804で構成される。投射光学系1803は、投射レンズを備えた複数の光学レンズで構成される。同図に示した光源光学系及び表示装置は図12-Aと図12-Bに於ける光源光学系及び表示装置1501,1602に適用できる。また光源光学系1801は図12-Dに示した光源光学系を用いれば良い。尚、表示装置1802にはカラーフィルター(図示しない)が設けられており、表示映像をカラー化している。

# [0103]

また図13-Bに示した光源光学系及び表示装置は図13-Aの応用例であり、カラーフィルターを設ける代わりに、RGBの回転カラーフィルター円板1805を用いて表示映像をカラー化している。同図に示した光源光学系及び表示装置は図12-Aと図12-Bに於ける光源光学系及び表示装置1501,1602に適用できる。

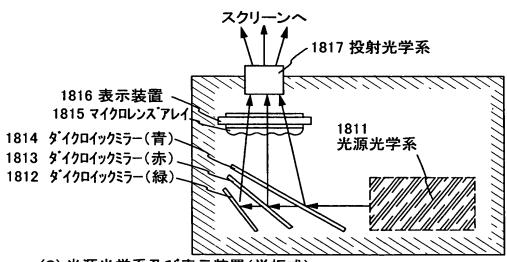

# [0104]

また図13-Cに示した光源光学系及び表示装置は、カラーフィルターレス単板式と呼ばれている。この方式は、表示装置1816にマイクロレンズアレイ1815を設け、ダイクロイックミラー(緑)1812とダイクロイックミラー(赤)1813とダイクロイックミラー(青)1814を用いて表示映像をカラー化している。投射光学系1817は、投射レンズを備えた複数の光学レンズで構成される。同図に示した光源光学系及び表示装置は、図12-Aと図12-Bに於ける光源光学系及び表示装置1501,1602に適用できる。また光源光学系1811としては、光源の他に結合レンズ及びコリメーターレンズを用いた光学系を用いれば良い。

#### [0105]

上記に記載した様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することが可能である。

# [0106]

#### 【発明の効果】

本発明は、マスクパターンに光強度低減手段を設置したゲート電極形成用フォトマスクまたはレチクルを適用するフォトリソグラフィ工程とドライエッチング工程とイオン注入工程から成る半導体装置の製造法であり、以下の効果が挙げられる。

# [0107]

任意のマスクパターンに光強度低減手段を設置可能である為、半導体装置の回路毎にGOLD構造とLDD構造とシングルドレイン構造のトランジスタを簡単に形成でき、半導体装置の原価低減と性能向上に有効である。

### [0108]

光強度低減手段の透過率と寸法を任意に設定可能である為、フォトリソグラフィ工程とドライエッチング工程を通して形成されるゲート電極の端部に於ける膜厚の薄くなったテーパー形状領域の膜厚と寸法を調整することができる。この為、前記テーパー形状領域のスルードープでイオン注入される低濃度不純物領域(nー領域またはpー領域)の濃度分布とチャネル方向寸法の最適化が可能となり、GOLD構造とLDD構造トランジスタの性能向上に有効である。

#### 【図面の簡単な説明】

- 【図1】 光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルのマスクパターン構成

- 【図2】 光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルを適用したGOLD構造多結晶シリコンTFTの形成法

- 【図3】 光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルを適用したGOLD構造とLDD構造とシングルドレイン構造多結晶シリコンTFTの回路毎形成法

- 【図4】 光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルを適用したGOLD構造とLDD構造とシングルドレイン構造多結晶シリコンTFTの回路毎形成法(簡便プロセス)

- 【図5】 液晶ディスプレイ全体の回路構成

- 【図6】 光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルを適用した液晶ディスプレイ製造法(1)

- 【図7】 光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルを適用した液晶ディスプレイ製造法(2)

- 【図8】 光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルを適用した液晶ディスプレイ製造法(3)

- 【図9】 光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルを適用した液晶ディスプレイ製造法(4)

- 【図10】光強度低減機能を有する補助パターンを設置したゲート電極形成用フォトマスクまたはレチクルを適用した液晶ディスプレイ製造法(5)

- 【図11】本発明の半導体表示装置への適用例(1)

- 【図12】本発明の半導体表示装置への適用例(2)

- 【図13】本発明の半導体表示装置への適用例(3)

#### 【符号の説明】

- 101:ゲート電極形成用フォトマスクまたはレチクル

- 102 : 遮光部

- 103 : スリット部(回折格子パターン)

- 104 : 透光部

- 105:ゲート電極形成用フォトマスクまたはレチクル

- 106 : 遮光部

- 107 : スリット部 (回折格子パターン)

- 108 : 透光部

- 109 :光強度分布

- 110:ゲート電極形成用フォトマスクまたはレチクル

- 111 : 遮光部

- 112 : 半透光部(半透膜)

- 113 : 透光部

- 114 : 光強度分布

- 201 : ガラス基板

- 202 : 多結晶シリコン膜

- 203 : ゲート絶縁膜

- 204:ゲート電極膜

- 205 :現像後レジストパターン

- 206 :ドライエッチング後レジストパターン

- 207:ゲート電極(第1のドライエッチング処理後)

- 208:ゲート絶縁膜(第1のドライエッチング処理後)

- 209 : 高濃度不純物領域 (n+領域)

- 210 : 低濃度不純物領域 (n-領域)

210a: Lov領域

210b: Loff領域

211:ゲート電極 (第2のドライエッチング処理後)

212:ゲート絶縁膜(第2のドライエッチング処理後)

301 : ガラス基板

302 : 多結晶シリコン膜

303:ゲート絶縁膜

304 : ゲート電極膜

305 ~307 :現像後レジストパターン

308 ~310 :ドライエッチング後レジストパターン

311 ~313 : ゲート電極 (第1のドライエッチング処理後)

314 ~316 : ゲート絶縁膜(第1のドライエッチング処理後)

317 : 高濃度不純物領域 (n+領域)

318 : 低濃度不純物領域 (n-領域)

318a: Lov領域

318b: Loff領域

319 : 高濃度不純物領域 (n+領域)

320 : 低濃度不純物領域 (n-領域)

321 : 高濃度不純物領域(n+領域)

322 ~324 : ゲート電極 (第2のドライエッチング処理後)

325 ~327 : レジストパターン

328 : ゲート電極(第3のドライエッチング処理後)

401 : ガラス基板

402 : 多結晶シリコン膜

403 : ゲート絶縁膜

404 : ゲート電極膜

405 ~407 :現像後レジストパターン

408 ~410 :ドライエッチング後レジストパターン

411 ~413 : ゲート電極 (第1のドライエッチング処理後)

414 ~416 : ゲート絶縁膜(第1のドライエッチング処理後)

417 : 高濃度不純物領域 (n+領域)

418 : 低濃度不純物領域 (n-領域)

418a: Lov領域

418b: Loff領域

419 : 高濃度不純物領域 (n+領域)

420 : 低濃度不純物領域 (n-領域)

421 : 高濃度不純物領域 (n+領域)

422 ~424 : ゲート電極 (第2のドライエッチング処理後)

501 : GOLD構造形成領域

502 : LDD構造形成領域

503 : シングルドレイン構造形成領域

601 : 画素領域

602 : シフトレジスタ回路

603:レベルシフタ回路

604 : バッファ回路

605 : サンプリング回路

606:シフトレジスタ回路

607 : レベルシフタ回路

608 : バッファ回路

701 : ガラス基板

702 : 下地膜

702a: 第1層目の酸化窒化シリコン膜

702b: 第2層目の酸化窒化シリコン膜

703 ~707 : 半導体層(多結晶シリコン膜)

708:ゲート絶縁膜(酸化窒化シリコン膜)

709 : ゲート電極膜 (TaN膜)

710a~715a:現像後レジストパターン

710b~715b:ドライエッチング後レジストパターン

716:ゲート絶縁膜(第1のドライエッチング処理後)

717 ~720 :ゲート電極(第1のドライエッチング処理後)

721 ~722 : 電極 (第1のドライエッチング処理後)

723 ~727 : 高濃度不純物領域 (n+領域)

728 ~731 : 低濃度不純物領域 (n-領域)

728a~730a: Lov領域

728b~730b: L of f 領域

732 ~735 : ゲート電極 (第2のドライエッチング処理後)

736 ~737 : 電極 (第2のドライエッチング処理後)

738:ゲート絶縁膜(第2のドライエッチング処理後)

739 ~742 : レジストパターン

743:ゲート電極(第3のドライエッチング処理後)

744 ~746 : レジストパターン

747 : 高濃度不純物領域(p+領域)

748 : 低濃度不純物領域 (p-領域)

749 : 高濃度不純物領域 (p+領域)

750:第1の層間絶縁膜(酸化窒化シリコン膜)

751:第2の層間絶縁膜(アクリル樹脂膜)

752 ~757 : 金属配線

758 :接続電極

759 : ゲート配線

760 ~761 :接続電極

762 : 画素電極 (ITO等)

801: nチャネル型TFT

802 : p チャネル型TFT

803: nチャネル型TFT

804:画素TFT

805 : 保持容量

806 : 駆動回路

807 : 画素領域

## 【図2】

# (A) ゲート電極形成用レジストパターンの形成

## (B) 第1のドライエッチング処理/イオン注入処理

503:シングルドレイン構造形成領域

502:LDD構造形成領域

501:GOLD構造形成領域

## 【図4】

## (A) ゲート電極形成用レジストパターンの形成

## (B) 第1のドライエッチング処理/イオン注入処理

## (C) 第2のドライエッチング処理/レジスト除去

## 【図5】

602:シフトレジスタ回路 (GOLD構造)

603:レベルシフタ回路 (GOLD構造)

604: バッファ回路(GOLD構造)

605: サンプリング回路 (LDD構造)

606:シフトレジスタ回路 (GOLD構造) 607:レベルシフタ回路 (GOLD構造) 608:バッファ回路 (GOLD構造)

601:画 素 領 域 (LDD構造)

【図6】

【図7】

【図8】

【図10】

## 【図11】

【図12】

(C)光源光学系及び表示装置(三板式)

【図13】

(A)光源光学系及び表示装置(単板式)

#### (B) 光源光学系及び表示装置(単板式)

(C) 光源光学系及び表示装置(単板式)

## 【書類名】要約書

#### 【要約】

【課題】半導体装置に於けるLDD構造とGOLD構造の形成は、従来、ゲート電極をマスクにセルフアラインで形成しているが、ゲート電極が2層構造となる為、成膜工程とエッチング工程が複雑になる。またドライエッチング等のプロセスのみでLDD構造及びGOLD構造の形成を行っている為、トランジスタ構造が全て同一構造となり、回路毎にLDD構造とGOLD構造とシングルドレイン構造を別々に形成することが困難である。

【解決手段】回折格子パターンまたは半透膜から成る光強度低減手段がマスクパターン端部からの距離に比例して増加する様に構成されたフォトマスクまたはレチクルを、ゲート電極形成用フォトリソグラフィ工程に適用する。これにより、ドライエッチング及びイオン注入工程を通し、半導体装置の回路毎にGOLD構造とLDD構造とシングルドレイン構造のトランジスタを形成することができる

#### 【選択図】 図1

## 出願人履歴情報

識別番号

[000153878]

1. 変更年月日

1990年 8月17日

[変更理由]

新規登録

住 所

神奈川県厚木市長谷398番地

氏 名

株式会社半導体エネルギー研究所